Successive Approximation Register Analog-to-Digital Converter

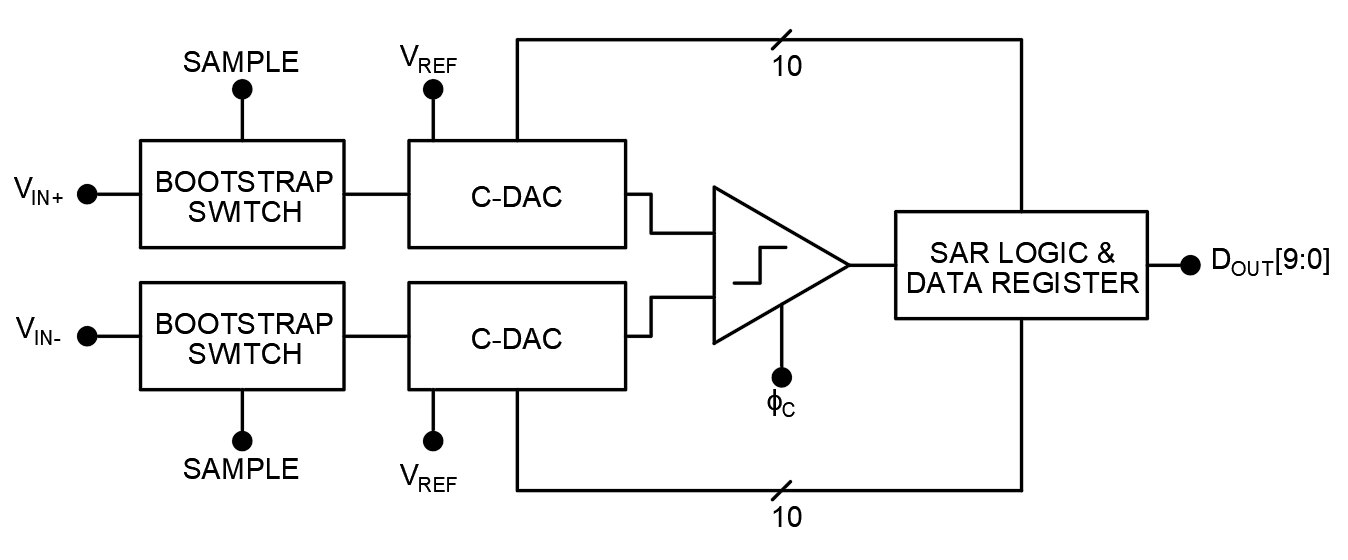

SAR ADC Block Diagram

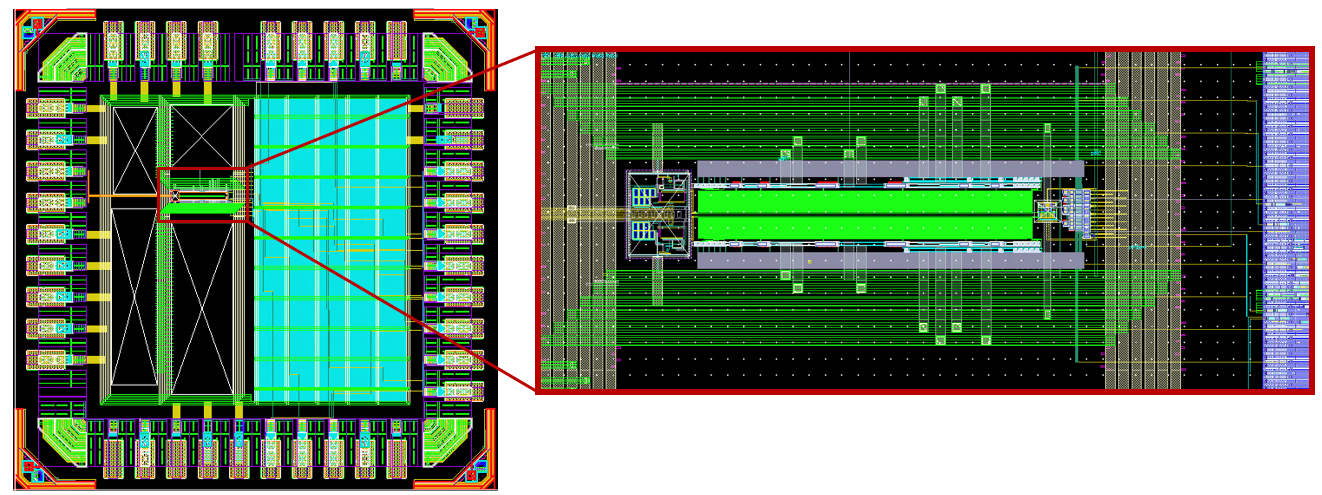

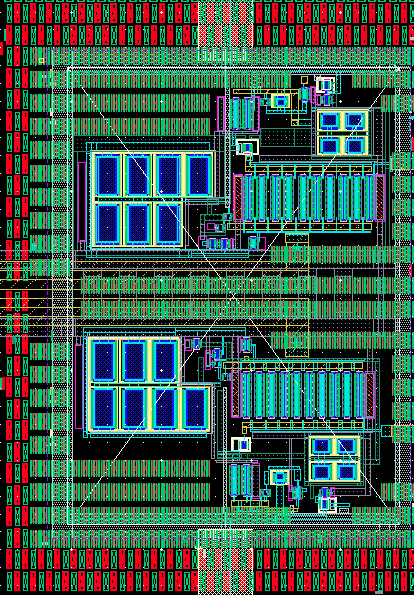

Chip Layout

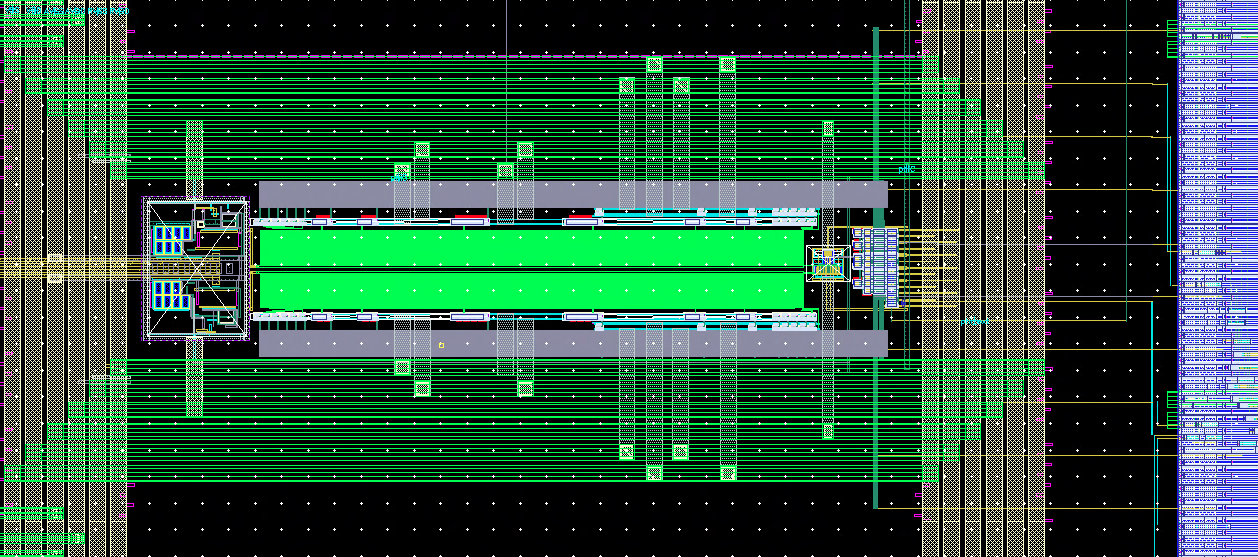

SAR ADC Components

SAR ADC Components

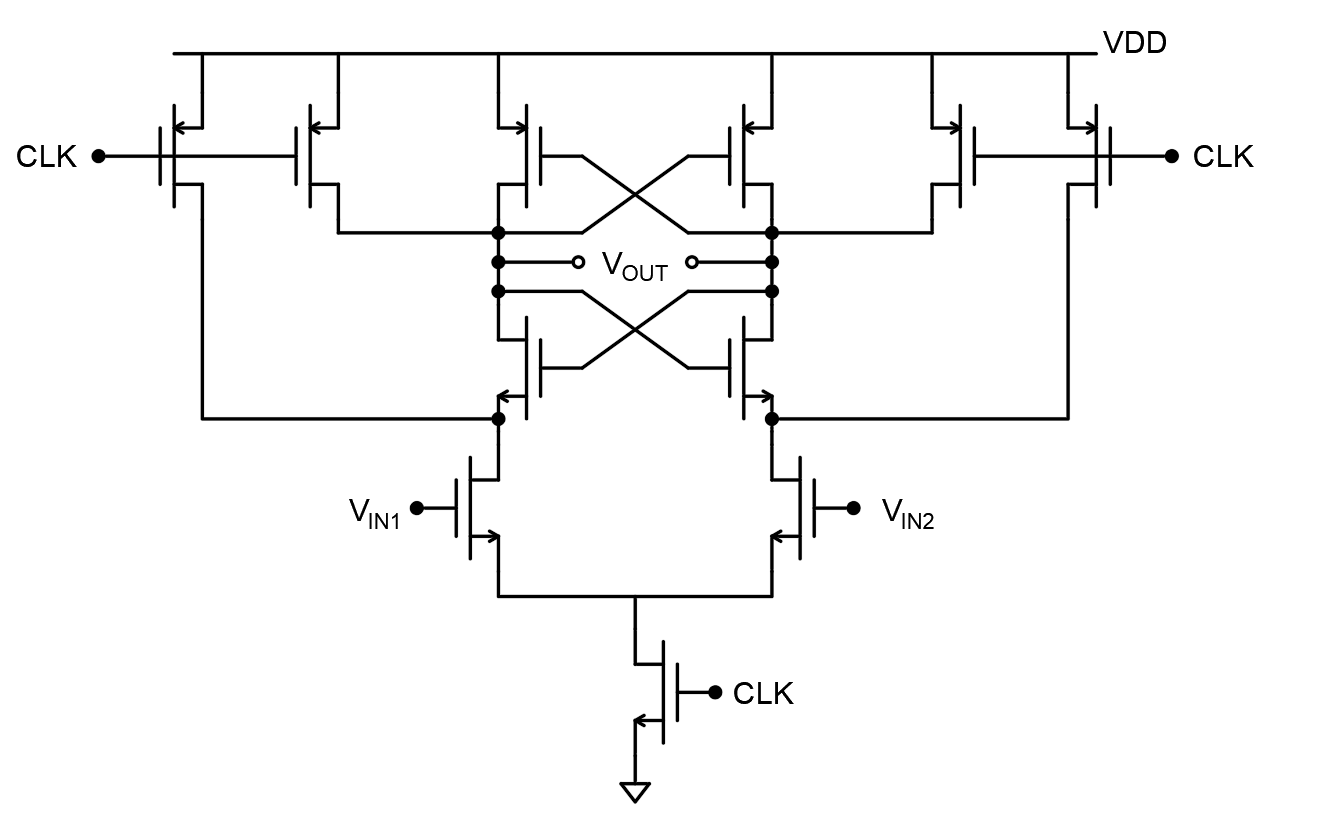

Comparator Schematic

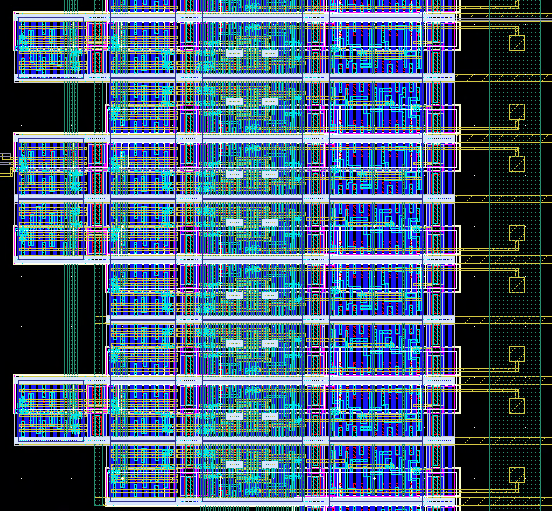

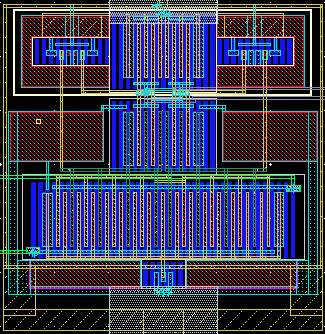

Comparator Layout

Bootstrap Switch Layout

Control Logic Layout